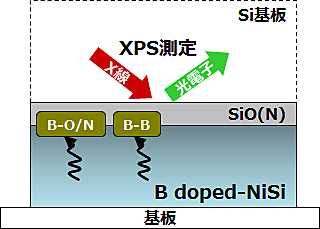

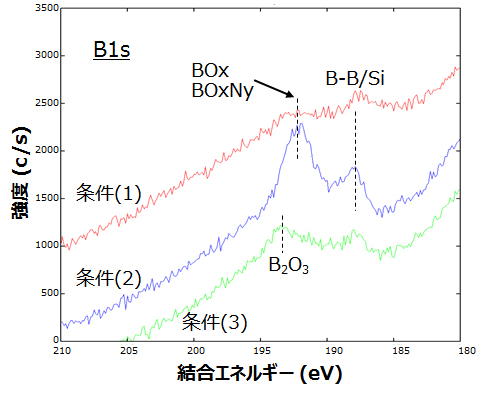

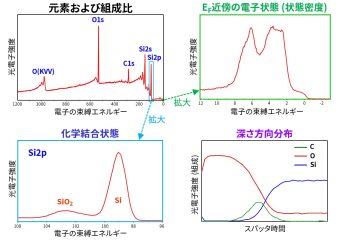

ゲート電極/酸化膜界面の不純物分析~裏面研磨技術を用いたXPS分析(Backside XPS)~Impurity-Analysis on the Gate Electrode / Oxide Interface using Backside XPS

ゲート電極/ゲート絶縁膜界面の不純物の分布や結合状態などを調べるためには1nm以下の深さ方向分解能が必要とされます。このような場合、裏面(ゲート絶縁膜側)からの測定を行うことで、より信頼性の高い解析が可能になります。XPSの検出深さは数nm以下と浅いので、Si基板部分を裏面から研磨やウェットエッチングにより除去してXPS測定を行います。